Q.No:1 GATE-2013

What should be the clock frequency of a \(6\)-bit A/D converter so that its maximum conversion time is \(32 \mu s\)?

(A)

\(1 MHz\)

(B)

\(2 MHz\)

(C)

\(0.5 MHz\)

(D)

\(4 MHz\)

Check Answer

Option B

Q.No:2 GATE-2014

The minimum number of flip-flops required to construct a mod-\(75\) counter is _____________________.

Check Answer

Ans 6.99-7.01

Q.No:3 GATE-2014

In order to measure a maximum of \(1 V\) with a resolution of \(1 mV\) using a \(n\)-bit \(A/D\) converter, working under the principle of ladder network, the minimum value of \(n\) is ______________.

Check Answer

Ans 9.99-10.01

Q.No:4 GATE-2015

Which one of the following \({\bf DOES \hspace{2mm} NOT}\) represent an exclusive OR operation for inputs \(A\) and \(B\)?

(A)

\((A+B)\overline{AB}\)

(B)

\(A\bar{B}+B\bar{A}\)

(C)

\((A+B)(\bar{A}+\bar{B})\)

(D)

\((A+B)AB\)

Check Answer

Option D

Q.No:5 GATE-2016

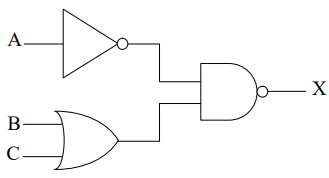

For the digital circuit given below, the output X is

(A)

\(\overline{\overline{A}+B\cdot C}\)

(B)

\(\overline{\overline{A}\cdot (B+C)}\)

(C)

\(\overline{A}\cdot (B+C)\)

(D)

\(A+\overline{(B\cdot C)}\)

Check Answer

Option B

Q.No:6 GATE-2017

The best resolution that a \(7\) bit A/D convertor with \(5 V\) full scale can achieve is _________ mV. (up to two decimal places).

Check Answer

Ans 39.30-39.50

Q.No:7 GATE-2017

The minimum number of NAND gates required to construct an OR gate is:

(A)

\(2\)

(B)

\(4\)

(C)

\(5\)

(D)

\(3\)

Check Answer

Option D

Q.No:8 GATE-2018

The logic expression \(\bar{A}BC+\bar{A}\bar{B}C+AB\bar{C}+A\bar{B}\bar{C}\) can be simplified to

(A)

\(A\) XOR \(C\)

(B)

\(A\) AND \(\bar{C}\)

(C)

\(0\)

(D)

\(1\)

Check Answer

Option A

Q.No:9 GATE-2018

In a 2-to-1 multiplexer as shown below, the output \(X=A_0\) if \(C=0\), and \(X=A_1\) if \(C=1\)

Which one of the following is the correct implementation of this multiplexer?

Check Answer

Option A

Q.No:10 GATE-2019

Consider the following Boolean expression:

\[

(\overline{A}+\overline{B})[\overline{A(B+C)}]+A(\overline{B}+\overline{C})

\]

It can be represented by a single three-input logic gate. Identify the gate.

(A)

AND

(B)

OR

(C)

XOR

(D)

NAND

Check Answer

Option D

Q.No:11 GATE-2019

For the following circuit, the correct logic values for the entries \(X_2\) and \(Y_2\) in the truth table are

(A)

1 and 0

(B)

0 and 0

(C)

0 and 1

(D)

1 and 1

Check Answer

Option A

Q.No:12 GATE-2020

Which one of the following is a universal logic gate?

(A)

AND

(B)

NOT

(C)

OR

(D)

NAND

Check Answer

Option D

Q.No:13 GATE-2020

Which one of the following is the correct binary euivalent of the hexadecimal F6C?

(A)

0110 1111 1100

(B)

1111 0110 1100

(C)

1100 0110 1111

(D)

0110 1100 0111

Check Answer

Option B

Q.No:14 GATE-2020

Consider a 4-bit counter constructed out of four flip-flops. It is formed by connecting the \(J\) and \(K\) inputs to logic high and feeding the \(Q\) output to the clock input of the following flip-flop (see the figure). The input signal to the counter is a series of square pulses and the change of state is triggered by the falling edge. At time \(t=t_0\) the outputs are in logic low state (\(Q_0=Q_1=Q_2=Q_3=0\)). Then at \(t=t_1\), the logic state of the outputs is

(A)

\(Q_0=1, Q_1=0, Q_2=0\) and \(Q_3=0\)

(B)

\(Q_0=0, Q_1=0, Q_2=0\) and \(Q_3=1\)

(C)

\(Q_0=1, Q_1=0, Q_2=1\) and \(Q_3=0\)

(D)

\(Q_0=0, Q_1=1, Q_2=1\) and \(Q_3=1\)

Check Answer

Option B

Q.No:15 GATE-2021

The below combination of logic gates represents the operation

(A)

OR

(B)

NAND

(C)

AND

(D)

NOR

Check Answer

Option B

Q.No:16 GATE-2021

The minimum number of two-input NAND gates required to implement the following Boolean expression is -------------

\[

Y=[A\bar{B}(C+BD)+\bar{A}\bar{B}]C

\]

Check Answer

Ans 3

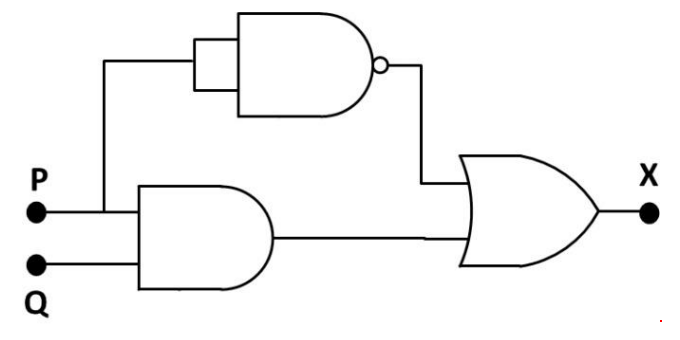

Q.No:17 GATE-2023

Which one of the following options is CORRECT for the given logic circuit?

(A)

P = 1, Q = 1; X = 0

(B)

P = 1, Q = 0; X = 1

(C)

P = 0, Q = 1; X = 0

(D)

P = 0, Q = 0; X = 1

Check Answer

Option D

Q.No:18 GATE-2024

The minimum number of basic logic gates required to realize the Boolean expression \( B \cdot (A + B) + A \cdot (\overline{B} + A) \) is _______ (in integer).

Check Answer

Ans 1

Q.No:19 GATE-2024

Consider the following circuit:

Suppose the input signal \( P \) is

and the input signal \( Q \) is

Which one of the following output signals is correct?

Check Answer

option a

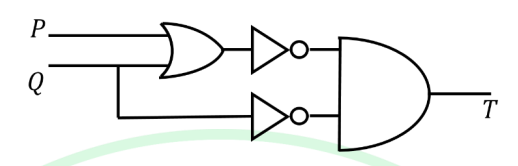

Q.No:20 GATE-2025

A logic gate circuit is shown in the figure below. The correct combination for the input \((P, Q)\) for which the output \(T = 1\) is

A) \((0,0)\)

B) \((0,1)\)

C) \((1,1)\)

D) \((1,0)\)

Check Answer

option A

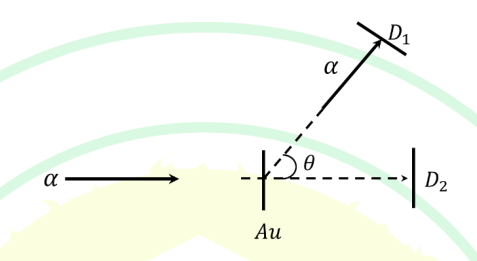

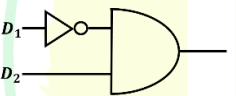

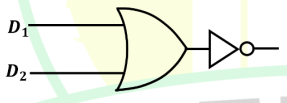

Q.No:21 GATE-2025

An \(\alpha\) particle is scattered from an Au target at rest as shown in the figure. \(D_{1}\) and \(D_{2}\) are the detectors to detect the scattered \(\alpha\) particle at an angle \(\theta\) and along the beam direction, respectively, as shown. The signals from \(D_{1}\) and \(D_{2}\) are converted to logic signals and fed to logic gates. When a particle is detected, the signal is 1 and is 0 otherwise. Which one of the following circuits detects the particle scattered at the angle \(\theta\) only?